芯片封裝技術的發展歷程

發布時間:

2022-07-08

摘 要

集成電路(IC)的核心是芯片。每塊集成電路芯片在使用前都需要封裝。封裝是IC芯片支撐、保護的必要條件,也是其功能實現的主要組成部分。隨著芯片及集成的水平不斷提高,電子封裝的作用正變得越來越重要。當今芯片封裝技術發展也越來越快,以滿足不斷快速增長的電子產品的需求。文章介紹了幾種芯片封裝技術的特點,并對未來的發展趨勢及方向進行了初步分析。從中可以看出IC芯片與微電子封裝技術相互促進,協調發展密不可分的關系。

1 什么是封裝

關注電腦核心配件發展的朋友都會注意到,廠商通常在推出革命性的CPU、內存或者芯片組時,都會強調產品采用了新的封裝形式。不過,很多人對封裝并不了解。那么究竟什么是封裝?它對電腦硬件的發展有什么意義?

封裝技術其實就是一種將集成電路打包的技術。拿我們常見的內存來說,我們實際看到的體積和外觀并不是真正的內存的大小和面貌,而是內存芯片經過打包即封裝后的產品。這種打包對于芯片來說是必須的,也是至關重要的。因為芯片必須與外界隔離,以防止空氣中的雜質對芯片電路的腐蝕而造成電氣性能下降。另一方面,封裝后的芯片也更便于安裝和運輸。由于封裝技術的好壞還直接影響到芯片自身性能的發揮和與之連接的PCB(Print Circuit Board,印刷電路板)的設計和制造,因此它是至關重要的。封裝也可以說是指安裝半導體集成電路芯片用的外殼,它不僅起著安放、固定、密封、保護芯片和增強導熱性能的作用,而且還是溝通芯片內部世界與外部電路的橋梁—芯片上的接點用導線連接到封裝外殼的引腳上,這些引腳又通過印刷電路板上的導線與其他器件建立連接。因此,對于很多集成電路產品而言,封裝技術都是非常關鍵的一環。芯片的封裝技術種類實在是多種多樣,諸如DIP、QFP、TSOP、BGA、CSP等等,一系列名稱看上去都十分繁雜,其實,只要弄清芯片封裝發展的歷程也就不難理解了。芯片的封裝技術已經歷經好幾代的變遷,技術指標一代比一代先進,包括芯片面積與封裝面積之比越來越接近,適用頻率越來越高,耐溫性能越來越好,以及引腳數增多,引腳間距減小,重量減小,可靠性提高,使用更加方便等等,都是看得見的變化,而促使這種變化的最根本因素來自于市場需求。從80年代中后期開始,電子產品正朝著便攜式/小型化、網絡化和多媒體化方向發展,這種市場需求對電路組裝技術提出了相應的要求:單位體積信息的提高(高密度化);單位時間處理速度的提高(高速化)。為了滿足這些要求,勢必要提高電路組裝的功能密度,這就成為了促進芯片封裝技術發展的最重要的因素。CPU和其他超大型集成電路在不斷發展,集成電路的封裝形式也不斷作出相應的調整變化,而封裝形式的進步又將反過來促進芯片技術向前發展。

2 開山鼻祖——DIP

DIP(Dual In-line Package)封裝又被稱為雙列直插式封裝,它應該是人們最為熟悉的封裝技術之一。早在4004、8086和8088等CPU中便得到了應用,如圖1。DIP有一個厚厚的外殼,從其兩側伸出兩列向下彎曲的外部引腳。DIP封裝的最大優點就是適合在PCB板上實現穿孔焊接,操作起來比較簡單,因此在現有半導體業中,DIP仍然占有一席之地,諸如某些BIOS芯片上就能見到它的身影。當然,DIP的缺點還是相當明顯的,芯片封裝面積和厚度都相對較大,由此也造成了整個芯片體積的增大。與此同時,外部引腳容易在芯片的插拔過程當中損壞,不太適用于高可靠性場合。此外,DIP封裝還有一個致命的缺陷,那就是它只適用于引腳數目小于100 的中小規模集成電路,對于發展迅猛的芯片領域來說,100引腳的限制是“致命”的,也正是這個原因,DIP慢慢退出了CPU封裝的舞臺。

3 早期強豪——QFP

當CPU發展到80286時代,封裝技術的鼻祖DIP已經不適合其需求了,QFP(Plastic Quad Flat Package,塑料方形扁平式封裝)出現了。與DIP相比,QFP同樣采用了引腳方式,不同的是改變了引腳從兩列伸出的方式,而是芯片四面全部有引腳,并且引腳從直插式改為了歐翹狀,如圖2,引腳間距可以更密,引腳可以更細。如此一來,在整個芯片面積不變的情況下可以容納更多的引腳,同時信號穩定性好,能夠滿足芯片高頻率工作的需求。正是因為這些優點,使得QFP封裝在80286時代得到了廣泛采用,并成為了當時高密度封裝的唯一選擇。

為了適應電路組裝密度的進一步提高,QFP的引腳間距目前已從1.27 mm發展到了0.3 mm。由于引腳間距不斷縮小, I/O 數不斷增加,封裝體積也不斷加大,給電路組裝生產帶來了許多困難,導致成品率下降和組裝成本的提高。另方面由于受器件引腳框架加工精度等制造技術的限制,0.3 mm已是QFP引腳間距的極限,這都限制了組裝密度的提高。0.5 mm引腳間距、304條引腳已經是目前電子封裝生產所能制造QFP封裝的最大值,若要容納更多的引腳,只有尋找更新的封裝,種種跡象表明QFP封裝已經走到了發展的盡頭。

4 一代強手——TSOP封裝技術

20世紀80年代,內存第二代的封裝技術TSOP(圖3)出現了,并得到了業界的廣泛認可。時至今日TSOP仍舊是內存封裝的主流技術。TSOP是“ThinSmall Outline Package”的縮寫,中文意思是薄型小尺寸封裝。TSOP封裝是在芯片的周圍做出引腳,采用SMT技術(表面貼裝技術)直接附著在PCB板的表面。TSOP封裝適合高頻應用環境,可靠性也比較高。同時TSOP封裝具有成品率高、價格便宜等優點,得到了極為廣泛的應用。

TSOP封裝方式中,內存芯片是通過芯片引腳焊接在PCB板上的,焊點和PCB板的接觸面積較小,使得芯片向PCB板傳熱就相對困難。而且TSOP封裝方式的內存在頻率超過150 MHz后,會產生較大的信號干擾和電磁干擾。由于這樣的特點,使得TSOP封裝在SDRAM、DDR SDRAM時代大放異彩,不少知名內存制造商如三星、現代、Kingston等目前都在采用這項技術進行內存封裝。但到了DDR2時代由于內存需要更高的頻率,所以TSOP才被BGA/CSP等封裝逐步替代。

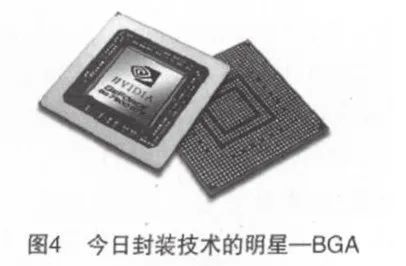

5 中流砥柱——BGA/CSP

20世紀90年代隨著集成技術的進步、設備的改進和深亞微米技術的使用,芯片集成度不斷提高,I/O 引腳數急劇增加,功耗也隨之增大,對集成電路封裝的要求也更加嚴格。為滿足發展的需要,在原有封裝方式的基礎上,又增添了新的方式-球柵陣列封裝,簡稱BGA(Ball Grid Array Package)。BGA封裝技術已經在GPU(圖形處理芯片)、主板芯片組等大規模集成電路的封裝領域得到了廣泛的應用。它的 I/O 引線以圓形或柱狀焊點按陣列形式分布在封裝下面,引線間距大,引線長度短,這樣BGA消除了精細間距器件中由于引線而引起的共面度和翹曲的問題。BGA技術的優點是可增加I/O數和間距,消除QFP技術的高引腳數帶來的生產成本和可靠性問題。如圖4所示的NVIDIA公司的GeForce圖形芯片(GPU)體現了當前工程技術的最高成就,相信看到芯片照片上那1144個焊球的人都會驚嘆不已。BGA一出現便成為CPU、圖形芯片、主板上南/北橋芯片等高密度、高性能、多引腳封裝的最佳選擇。

概括起來,和QFP相比,BGA的優點主要有以下幾點:

(1) I/O 引線間距大(如1.0 mm,1.27 mm),可容納的 I/O 數目大(如1.27 mm間距的BGA在25 mm邊長的面積上可容納350個 I/O ,而0.5 mm間距的QFP在40 mm邊長的面積上只容納304個 I/O )。

(2)封裝可靠性高(不會損壞引腳),焊點缺陷率低,焊點牢固。

(3)管腳水平面同一性較QFP容易保證,因為焊錫球在溶化以后可以自動補償芯片與PCB之間的平面誤差。

(4)回流焊時,焊點之間的張力產生良好的自對中效果,允許有50%的貼片精度誤差。

(5)有較好的電特性,由于引線短,導線的自感和導線間的互感很低,頻率特性好。

(6)能與原有的SMT貼裝工藝和設備兼容,原有的絲印機、貼片機和回流焊設備都可使用。

BGA的興起和發展盡管解決了QFP面臨的困難,但它仍然不能滿足電子產品向更加小型、更多功能、更高可靠性對電路組件的要求,也不能滿足硅集成技術發展對進一步提高封裝效率和進一步接近芯片本征傳輸速率的要求,所以更新的封裝CSP(Chip Size Package,芯片尺寸封裝)又出現了,它的英文含義是封裝尺寸與裸芯片相同或封裝尺寸比裸芯片稍大。日本電子工業協會對CSP規定是芯片面積與封裝尺寸面積之比大于80%。CSP與BGA結構基本一樣,只是錫球直徑和球中心距縮小了、更薄了,這樣在相同封裝尺寸時可有更多的 I/O 數,使組裝密度進一步提高,可以說CSP是縮小了的BGA。圖5展示的是行業領先內存廠商Kingmax生產的基于CSP封裝技術的內存芯片。

CSP之所以受到極大關注,是由于它提供了比BGA更高的組裝密度,而比采用倒裝片的板極組裝密度低。但是它的組裝工藝卻不像倒裝片那么復雜,沒有倒裝片的裸芯片處理問題,基本上與SMT的組裝工藝相一致,并且可以像SMT那樣進行預測和返工。正是由于這些無法比擬的優點,才使CSP得以迅速發展并進入實用化階段。目前日本有多家公司生產CSP,而且正越來越多地應用于移動電話、數碼錄像機、筆記本電腦等產品上。從CSP近幾年的發展趨勢來看,CSP將取代QFP成為高I/O引線IC封裝的主流。

6 主流C PU 封裝技術——PGA

PGA(Pin Gird Array Package,格柵陣列封裝)是最常見的CPU封裝方式之一,目前大多數CPU均采用此類封裝方式,如圖6。PGA封裝最大的優點是安裝方便,適用于高頻率芯片。PGA封裝在芯片下方圍著多層方陣形的插針,每層方陣形插針是沿芯片的四周、間隔一定距離排列的,根據針腳數目的多少,可以圍成2~6圈。PGA封裝缺點是耗電量較大。

從486時代開始,出現了一種名為ZIF(Zero Insertion Force Socket,零插拔力插槽)的CPU插槽,使用PGA封裝的CPU可以很輕松地插入這種插槽中,并將扳手壓回原處,利用插槽本身的特殊結構產生的擠壓力,使CPU的針腳與插槽“親密”接觸。反之,拆卸CPU時只須將插槽的扳手輕輕抬起,則壓力解除,CPU即可輕松取出。這種插槽一直沿用至今,專門用于安裝和拆卸PGA封裝的CPU。

7 高性能芯片封裝首選——LGA

LGA全稱是Land Grid Array,直譯就是柵格陣列封裝。這種封裝技術實際上是PGA 封裝的改良。和PGA封裝相比,LGA首先將底部的所有引腳去掉,轉而變成了平面上的大量觸點,如圖7。這樣一來就徹底消除了PGA封裝引腳密度增加之后相互的信號干擾問題。LGA封裝可以直接上錫裝在PCB上,也可以通過LGA插座與芯片連接,在采用這樣的連接方式后,芯片與PCB的距離得以顯著縮短,使得LGA封裝的電氣性能更好于PGA。

正是因為LGA封裝擁有更為優秀的特性,使得當今各種高密度的CPU、FPGA、DSP等芯片都紛紛轉向LGA封裝,其中Intel早在2005年就將旗下的Pentium、Celeron處理器轉為LGA封裝,從而保證CPU頻率的提升不受封裝電氣性能的阻礙,其它芯片廠商也開始全面為用戶提供LGA封裝的產品。毫無疑問,LGA封裝將會在未來逐步取代PGA,成為主流的芯片封裝形式。

8 新興力量—MCM

BGA封裝比QFP先進,但它的芯片面積/封裝面積的比值仍很低。這時有人設想,當單芯片一時還達不到多種芯片的集成度時,能否將多個集成電路芯片在高密度多層互聯基板上用表面安裝技術(SMT)組裝成為多種多樣電子組件、子系統或系統。由這種想法產生出多芯片組件MCM(Multi Chip Model)。它將對現代化的計算機、自動化、通訊業等領域產生重大影響。Intel推出的新一代處理器酷睿2雙核處理器采用了MCM技術,擁有兩個處理核心,能更好地運行多個程序,現在酷睿2四核處理器也已經開始大量上市,從這里開始,Intel CPU封裝歷史又要邁開新的一步。

MCM的特點有:

(1)封裝延遲時間縮小,易于實現組件高速化;

(2)縮小整機/組件封裝尺寸和重量,一般體積減小1/4,重量減輕1/3;

(3)可靠性大大提高;

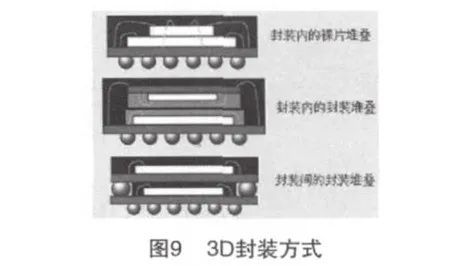

9 封裝極致—3D 封裝技術

在上述文章中我們介紹的所有封裝技術,伴隨著芯片體積的增加最后封裝出來的產品面積也將會顯著增加。那在現有技術條件和有限的空間內,如何進一步提升晶體管的密度?業界想到了讓芯片縱向發展的辦法。3D封裝技術也因此誕生。3D封裝可以通過兩種方法實現:封裝內的裸片堆疊和封裝堆疊,如圖8,封裝堆疊又可分為封裝內的封裝堆疊和封裝間的封裝堆疊。兩種方法各有利弊。總體上說:

(1)封裝堆疊已經研發出不同的形式,這種封裝使得能夠堆疊來自不同供應商和混合集成電路技術的裸片,也允許在堆疊之前進行預燒和檢測。

(2)封裝堆疊包括翻轉一個已經檢測過的封裝,并堆疊到一個基底封裝上面,后續的互連采用線焊工藝。封裝堆疊的裝配過程類似于裸片堆疊CSP。封裝堆疊在印制板裝配的時候需要另外的表面安裝堆疊工藝。

(3)因為裸片堆疊CSP在開發Z方向空間(即高度)的同時還保持了其X和Y方向上的元件大小(厚度即使增加也是非常小),這種封裝已經被很多手機應用所接受。裸片堆疊CSP封裝的主要缺點在于堆疊中的一層集成電路出現問題,所有堆疊的裸片都將報廢,但毫無疑問裸片堆疊能夠獲得更為緊湊的芯片體積。

在裸片堆疊技術領域,業界最大的內存、閃存制造商三星對此有著極為深入的研究。早在2006年初,三星就宣布了獨家用于內存芯片的3D封裝技術。三星公司將這種新技術命名為“晶圓級的堆疊工藝”,簡稱WSP。現有的芯片封裝依賴于對印刷電路板的有線連接,這種有線連接需要互連之間存在空間,以消除干擾,但是在制造高密度內存之時,這種空間會成為制約因素。三星宣布的“通過矽”的互相連接技術,本質上是激光在內存芯片之間打孔,然后以導體材料填充這些孔,以產生垂直互連效果。三星公司則在一個封裝中堆疊了8個2 GB NAND芯片。這種容量16 GB的NAND芯片高度只有半個毫米(圖9)。

由于各種裸片堆疊技術的逐步成熟,在未來許多3D封裝都將會轉向裸片堆疊以進一步降低體積。我們甚至可以期待在不久的將來通過3D封裝技術,一張SD卡的容量可以輕松突破20GB!

10 結語

究竟一片簡單的芯片凝結了多少智慧我們無從考究,但要讓一片芯片正常運行往往需要成千上萬種技術的良好配合以及正常工作。作為芯片制造中不可或缺的封裝技術,每次封裝的進化都將會帶動整個芯片制造行業的巨大發展。芯片封裝就像是半導體行業的風向標,從一部封裝技術的簡史中,我們就得以窺探半導體技術的發展足跡。

關鍵詞:

相關新聞